上海集成电路技术与产业促进中心(ICC)是科技部授牌的国家集成电路设计产业化基地,工信部授牌的国家“芯火”计划双创平台,肩负着推动上海乃至全国集成电路设计业发展的历史重任,着力于建设和发挥专业技术服务、高新技术领域项目管理、产业化促进三大功能。建设有集成电路设计专业技术服务平台和RFID专业技术服务平台,及一个中国合格评定国家认可委员会(CNAS)认可实验室。为业界提供多项目晶圆(MPW)、工程批及量产流片服务、EDA/IP服务、RFID、移动支付、物联网、USB等检测服务、及人才培养、行业技术信息研究分析等服务。

【命题一:芯来科技】:

芯来科技是中国领先的RISC-V处理器内核IP和解决方案公司,持续聚焦RISC-V处理器内核研发,赋能本土RISC-V产业生态。芯来科技的处理器产品具备高性能、低功耗和易于使用的特点,在性能、面积、功耗、成熟度、价格及开发平台等方面具有优势,处于中国RISC-V嵌入式处理器研发与产业化的最前列。已推出的100,200系列RISC-V处理器内核IP,对标传统8位、16位以及ARM的M系列处理器内核,已经应用在兆易、晶晨等多家知名客户量产产品中。新发布的300,600以及在研的900系列产品,全面支持 Linux与高性能边缘计算与控制。除了标准的处理器产品外,公司还提供针对汽车、工业控制和AI等领域的RISC-V处理器以及配套解决方案。芯来科技目前是RISC-V基金会银级会员、中国RISC-V产业联盟副理事长单位、中国开放指令生态(RISC-V)联盟会员单位。

一、赛题

RISC-V MCU 嵌入式开发

二、背景

随着电子技术的不断发展,出现了各种各样的智能设备,人们生活得到了极大的便利,其中嵌入式设备以其功耗低、体积小等优点得到了广泛的应用。

三、描述及要求

采用基于 RISC-V内核的GD32VF103 通用MCU,以万物智能互联为主题, 针对智能家居、智慧城市、可穿戴设备、智能驾驶、智能控制等一些热门应用的相关课题进行开放性的创新产品、服务和技术的研究与应用。

1. 使用Nuclei RV-STAR硬件开发板

2. 使用Nuclei SDK开源软件平台

四、例题(供参考,不限于此):

1.运动控制方向

外扩电机驱动电路,使用GD32VF103 MCU实现永磁同步电机/无刷直流电机的闭环控制(转速/位置)。通过一定人机交互的实现,完成电机的远程精准控制。

2.音频处理方向

使用GD32VF103 MCU实现音频数据的解码,并通过外扩的音频播放电路实现音乐播放。音频数据的获取可以来自于本地存储(SD卡)或者通过网络抓取下载(外扩wifi模块)。

3.智能家居方向

外接多种环境监测传感器(温湿度、光线等)及环境控制设备(小风扇、电动窗帘等),在GD32VF103 MCU上运行常见的嵌入式实时操作系统(例如FreeRTOS/UCOSII/RT-Thread等)进行整体的任务调度管理。

五、软硬件开发平台:

1.Nuclei RV-STAR开发板

https://www.riscv-mcu.com/quickstart-quickstart-index-u-RV_STAR.html

https://doc.nucleisys.com/nuclei_board_labs/

2.Nuclei SDK软件开发平台

https://doc.nucleisys.com/nuclei_sdk/

https://github.com/Nuclei-Software/nuclei-sdk

3.Nuclei Studio/ Segger Embedded Studio/ PlatformIO集成开发环境

https://www.nucleisys.com/download.php

https://www.riscv-mcu.com/quickstart-quickstart-index-u-RV_STAR_PROJECT.html

https://www.nucleisys.com/upload/file/2020/02/1581671399-5500.pdf

https://platformio.org/platforms/nuclei/

六、作品提交要求

1.详细设计文档和完整软件代码。

2.作品讲解及展示PPT。

3.作品展示视频。视频时长不超过10分钟,文件大小100MB以内。

4.所有获奖作品均可共享至RVMCU开放社区。

七、评审点

指标 | 评审标准 |

创意与创新 | 作品创意构想是否新颖巧妙,设计思路是否有突破性和创新性。 |

先进性与复杂度 | 作品设计是否采用了热门的前沿技术,是否具有一定复杂度。 |

完整度及可展示性 | 作品功能演示是否成功及完整。 |

实用性 | 作品是否切实解决了实际问题,是否具有广阔的应用前景。 |

推广性 | 作品是否充分使用处理器的特性完成关键功能的实现和性能的提升,是否对Nuclei开源软件平台产生一定的贡献。 |

八、技术答疑联系人

联系人:胡灿

联系方式:15071260198

邮箱:canhu@nucleisys.com

【命题二:SiFive】

SiFive是基于免费且开放的RISC-V指令集架构的商业化处理器核心IP、开发工具和芯片解决方案的领导者。 在RISC-V开创者和业内资深专家组成的团队领导下,SiFive帮助SoC设计人员缩短产品上市时间,以及通过定制的开放式架构处理器内核降低成本,同时,使系统设计人员能够构建基于RISC-V的定制半导体,从而实现芯片优化。

上海赛昉科技有限公司成立于2018年8月24日,公司基于RISC-V的开源生态并在RISC-V开创者和业内资深专家组成的团队领导下,利用领先的RISC-V内核定制技术和敏捷设计方法,成为具有国内自主可控,有龙头作用的RISC-V解决方案提供商;同时利用自主知识产权针对AI-IOT的关键应用领域,通过平台化、模板化的设计理念,实现垂直领域的核心技术整合,提供相关领域的系列化芯片及其解决方案,创造一种新的商业模式,成为对应领域的技术主导者和芯片与方案的主流供应商。

一、赛题

基于SiFive-E21处理器核的人工智能SoC 设计

二、赛题要求

利用SiFive E21处理器在Xilinx或Intel的可编程逻辑平台上构建片上系统,实现音频或图像信号的采集和数据后处理。需要在SoC中实现专门的硬件加速器以提高系统的性能,实现系统对信号的人工智能处理和分析,要求系统具有创新性、实用性和一定的市场前景。具体要求如下:

1. 选题内容限于智能语音、图像或视频数据分析等应用,SoC本身需要具备人工智能处理能力,将人工智能算法加速器置于在FPGA开发板内。

2. 使用上海赛昉科技提供的E21处理器IP,在Xilinx或Intel的FPGA平台上构建简单的片上系统。系统至少包含:

1) Xilinx或Intel的FPGA平台不得内置任何处理器内核。

2)FPGA平台内必须使用SiFive E21处理器;

3) 以可读Verilog语言实现DMA/(Q)SPI/I2C/I2S/UART/GPIO/RTC/WDT/Timer/PWM等AMBA接口的外设,如全部或部分使用FPGA自带如Vivado外设IP或其他语言所编译的可综合Verilog语言实现会降低分数;

4) 外设数量不限,够系统演示用即可,但数量多寡会影响基础设计部分的评分;

5)利用片上或板上的存储器资源实现的SoC所需的ROM与RAM;

6) 软件部分需要以RISC-V编程方法,使用RISC-V编译工具Freedom Studio IDE编写外设驱动程序并生成软件程序;

7)芯片外部的GPIO引脚连接到FPGA板上的LED与按键并以裸跑软件控制,确保程序正确运行。

3. 需要在FPGA平台上利用板载资源或扩展的硬件资源,为SoC添加信号采集/预处理/人机交互等接口模块;

4. 为SoC添加具备执行人工智能或机器学习等智能处理算法硬件加速器,采用独立加速器在设计中应突出硬件加速器对系统的优化效果

5. 以软硬协同的设计思路对SoC进行合理的软硬件任务划分,分析并说明软硬件任务划分的合理性。

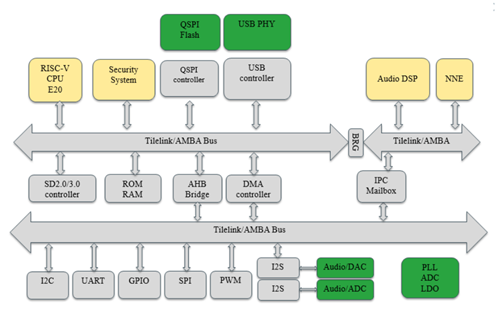

6. 智能语音SoC参考系统框图

三、作品提交

1) 设计报告包含系统设计方案,需有系统功能介绍、系统架构图、软硬件功能划分、加速器详细设计等,以及功能仿真及测试结果图、系统展示图片、视频。

2) 作品展板与PPT,内有团队介绍、设计报告重点、技术创新点与项目研发进度等。

四、设计数据

1)软硬件设计源代码、仿真和测试结果

2)现场答辩和现场利用FPGA开发板演示SoC的人工智能功能

五、评分规则

内容 | 分值 | 评分依据 |

1.完成E21片上系统的基础设计 | 50分 | 正确获得E21 IP,使用AMBA总线连接存储器与Verilog实现的外设IP;在FPGA硬件平台上实现片上系统,正确编译驱动程序、下载软件程序,现场编程调试。通过按键改变LED等的闪烁方式或频率确认系统正常运行。 |

2.完成信号采集或通信模块的数字接口设计,并作为与E21片上系统的外设 | 10分 | 详实规范的设计文档; 硬件接口设计的功能仿真结果; 编写软件成功实现语音或图像信号采集。 |

3.人工智能加速器的设计与实现 | 20分 | 加速器设计的功能仿真结果; 人工智能算法的详细设计方案。 |

4.系统优化分析,根据PPT、设计文档和视频演示展示研发成果 | 10分 | 针对SoC功耗、面积等进行优化,给出优化前后的对比结果; 系统的完整性、鲁棒性、创新性和市场潜力; 指出目前设计的不足和可以进一步优化的方向。 |

5.答辩和现场演示 | 10分 | 答辩和问答表现 |

六、其他注意事项

1) 参赛所选用的FPGA开发平台限制Xilinx或Intel FPGA开发板,参赛队伍使用自己的FPGA开发板进行报名流程。

2)参赛队伍需要提交一份参赛计划书给到邮箱arthur.chen@sifive-china.com,邮件主题为“第十五届中国研究生电子设计竞赛RISC-V杯-SiFive赛题计划书”。计划书具体描述项目开发思路和以往相关开发成果,上海赛昉科技会在进一步沟通后确认计划可行性。微信新浪微博QQQQ空间豆瓣网百度贴吧

七、技术答疑联系方式

联系人:陈宏铭

联系方式:13816808707

邮箱:arthur.chen@starfivetech.com

【奖项设置】

“芯火计划”专项赛团队,免费提供专业技术指导,同时拥有四次获奖机会:

1.可以参与专项赛单独评奖(一等奖1个:奖金8000元/队,二等奖2个,奖金3000元/队,三等奖5个,奖金1000元/队);

2.可以根据参赛项目类别参加第十五届中国研究生电子设计竞赛评奖;

3.优先推荐参加第三届中国研究生创芯大赛;

4.优先推荐参加第二届中国研究生人工智能创新大赛。

上海赛区企业命题报名方式(仅限上海赛区)

第一步

登陆“中国研究生创新实践系列大赛管理平台“官网-注册/登录报名系统:

第二步

“赛题”选择“开放命题”

第三步

依照本团队所做研究方向,从7大主题中进行选择,如图

第四步

继续完成后续系统后,邮件发送报名信息:“团队名+队长+联络方式+作品名(如:勇敢的心-王五-188XXXXXXXX-基于人工智能系统XXX)”至上海赛区对应的企业命题联络人邮箱:

命题一联络人:胡灿;邮箱:canhu@nucleisys.com

命题二联络人:陈宏铭;邮箱:arthur.chen@starfivetech.com

“兆易创新杯”第十五届中国研究生电子设计竞赛

“Arm杯”上海赛区执委会

2020年6月1日